在《編碼:隱匿在計(jì)算機(jī)軟硬件背后的語言》一書的第13章和第14章中,作者深入探討了二進(jìn)制減法器和1位存儲器的原理,這些組件構(gòu)成了計(jì)算機(jī)硬件邏輯的基礎(chǔ)。這些內(nèi)容不僅揭示了計(jì)算機(jī)內(nèi)部如何執(zhí)行基本運(yùn)算,還展示了如何通過簡單電路實(shí)現(xiàn)數(shù)據(jù)的持久存儲。

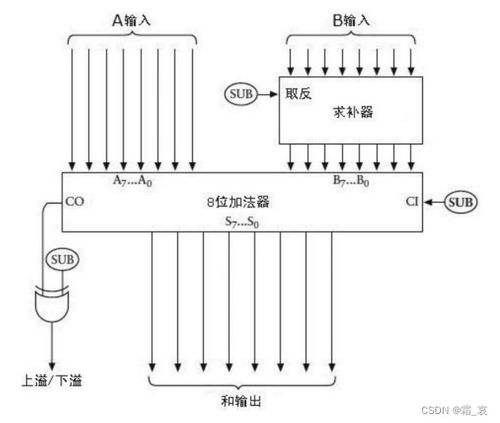

第13章聚焦于二進(jìn)制減法器。與二進(jìn)制加法類似,減法在計(jì)算機(jī)中同樣通過邏輯電路實(shí)現(xiàn)。二進(jìn)制減法器基于半減器和全減器設(shè)計(jì),利用異或門、與門和非門來處理借位操作。例如,半減器接收兩個(gè)輸入位(被減數(shù)和減數(shù)),輸出差值和借位;全減器則擴(kuò)展至處理來自低位的借位輸入。通過級聯(lián)多個(gè)全減器,可以構(gòu)建多位的二進(jìn)制減法器,實(shí)現(xiàn)如A-B的運(yùn)算。這一設(shè)計(jì)體現(xiàn)了計(jì)算機(jī)如何將數(shù)學(xué)問題轉(zhuǎn)化為硬件邏輯,是理解算術(shù)邏輯單元(ALU)的關(guān)鍵。

第14章則轉(zhuǎn)向1位存儲器,這是計(jì)算機(jī)存儲系統(tǒng)的基石。1位存儲器通常由邏輯門電路(如與門、或門和非門)構(gòu)成,能夠存儲單個(gè)比特(0或1)的信息。常見的實(shí)現(xiàn)包括RS觸發(fā)器(復(fù)位-置位觸發(fā)器),它通過兩個(gè)交叉耦合的NOR門或NAND門來保持狀態(tài),直到外部信號觸發(fā)改變。例如,當(dāng)設(shè)置輸入激活時(shí),輸出為1;當(dāng)復(fù)位輸入激活時(shí),輸出為0。這種簡單的存儲機(jī)制允許計(jì)算機(jī)臨時(shí)保存數(shù)據(jù),為更復(fù)雜的存儲單元(如寄存器、內(nèi)存)提供基礎(chǔ)。

這兩章內(nèi)容強(qiáng)調(diào)了計(jì)算機(jī)軟硬件的緊密聯(lián)系:二進(jìn)制減法器展示了硬件如何執(zhí)行基本算術(shù),而1位存儲器則揭示了數(shù)據(jù)持久化的原理。理解這些底層邏輯,有助于我們把握計(jì)算機(jī)的整體架構(gòu),從簡單的電路到復(fù)雜的處理器設(shè)計(jì)。這些知識不僅適用于硬件工程,還為軟件優(yōu)化和系統(tǒng)設(shè)計(jì)提供了深刻洞見。